把很多干扰频率滤除,而且相对而言超外差方案如果不考虑对别人的发射影响,超外差方案只在接收的抗干扰上有优势。

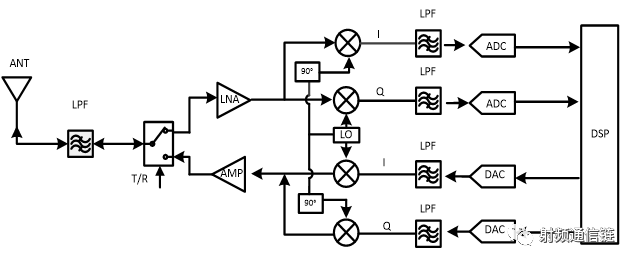

零中频架构,将射频直接变成基带信号。所以零中频在尺寸、功耗上都很有优势。这也是方案时选择这个方案最重要的考虑。

因为零中频是正交变换,所以硬件的不一致,会导致零中频方案出现因为差分正交不平衡带来的频谱拓展。

低中频方案,为了规避零中频存在的问题,在ADC之前做了一次变频处理。因为是在FPGA做处理,所以相对超外差方案比,尺寸和功耗有优势。

侧重射频指标的一般用超外差,因为中频滤波器的存在,可以比较容易的实现高指标。

低中频的方案主打的也是功耗和尺寸,对于一些实时更新的收发设计,零中频设计在直流和偏差会存在差异,一般采用低中频方案来规避。

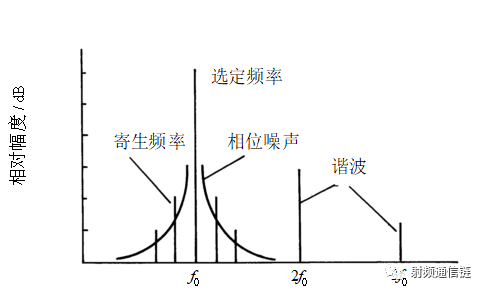

锁相环的选型关系到发射和接收链路的关键指标,锁相环也是杂散的关键来源之一。所以锁相环的选择至关重要。

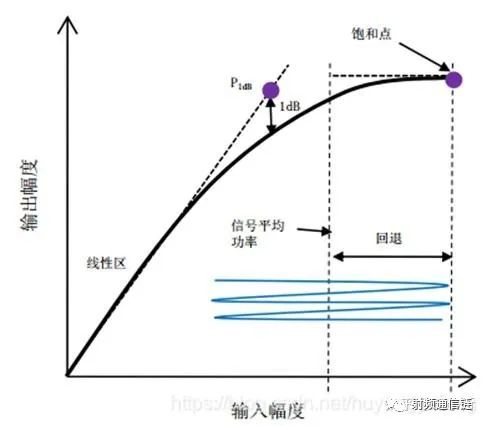

之前的文章我们讲过,收发电路的设计就是设计整个收发系统的线性,整个收发电路中用的最多的也是放大器

现有的混频器的p-1基本上都在10左右,混频器也是超外差方案相位噪声的卡点处。

根据混频器的p-1和频率源的相位噪声,就可以设计混频前后的增益,动态范围,滤波器,宽带噪声等指标的设计分配。

外围电路的选择和设计主要是为了完成主要电路服务,在设计上按照需求选择合适的电路。

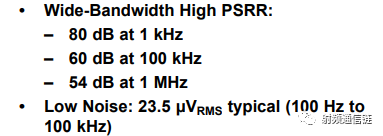

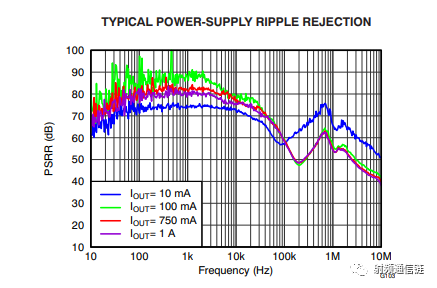

还有一个杂散的关键来源就是电源,电路中因为P-1和器件的应用问题,所需要的电压也不同,为了提升整个设计的效率,通常会使用DC-DC。

而在DCDC的使用过程中,就可能会出现开关频率和cross频率,这两种频率会调制到锁相环和放大器上,形成杂散输出。

所以在DC设计时,需要注意DC的PSRR。一般来说杂散要求60dB,PSRR的要求就需要高于杂散的设计要求。

关键器件选择完毕,就需要设计原理图了,原理图的设计原则是能用简单设计就用简单设计,能用熟悉器件就用熟悉的器件。

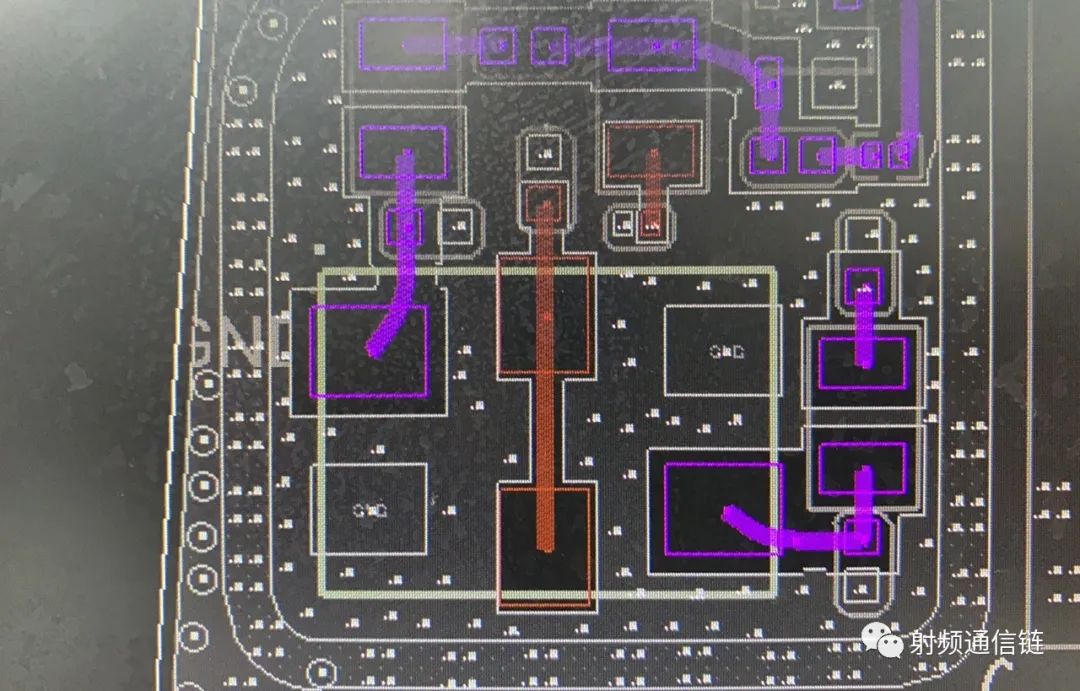

PCB的设计原则是敏感器件离电源越远越好,注意关键走线的阻抗和隔离。另外要强调一点,很多设计都说要数字地和模拟地隔离,对于射频PCB布局来说,最好一块地,隔离地可能会出现不想要的东西。

问题一般来说都没有想象的复杂,找到了之后可能就是一个走线,一个电感,甚至一个过孔。

Copyright © 2019-2023 完美集团有限公司 版权所有